#### **VORTRAG**

**Andreas Kraus**Geschäftsführender

Gesellschafter

"Sinn und Möglichkeiten der elektrischen Bagruppenprüfung"

1992

Gründung Kraus Hardware Entwicklung Entwicklung der ADwin MSR-Systeme

1998

Umfirmierung in Kraus Hardware GmbH

seit 2001

EMS-Dienstleistungen

2002

Damfhphasenlötanlage (Erweiterung im Jahr 2013)

seit 2007

ICT Flying Probe und Rework von Baugruppen

2009

Neues Firmengebäude

seit 2009

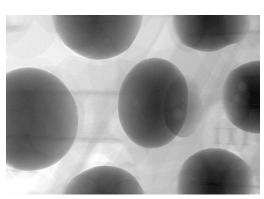

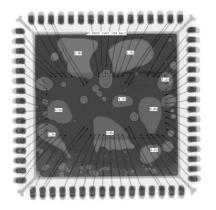

Röntgenanalyse 2D (Erweiterung im Jahr 2012)

2009

Zertifizierung nach ISO 9001:2008

seit 2011

Boundary Scan von Baugruppen

seit 2012

Erweiterung der Röntgenanalyse um 3D (CT)

seit 2013

Erweiterung des Damfphasenlötens – neue Anlage mit Vakuum

seit 2014

Selektivlöten

seit 2015

**Einführung Traceability**

2017

Erweiterung der Bestückungskapazität und Installation des vollautomatischen Rollenlagers

2018

AOI 3D/2D, Re-Zertifizierung nach ISO 9001:2015, Baugruppenreinigungsanlage und Bauteilgurtung

2020

MOPA Faserlaser(system) zum Beschriften und Schneiden

#### Geschäftsfelder

zweigeteiltes Angebotsspektrum

## Dienstleistungen 65%

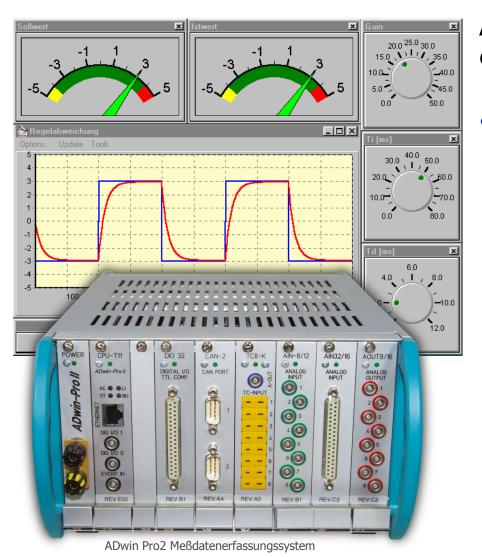

## **ADwin**

Meßdatenerfassungssysteme

Eigene Produkte 35%

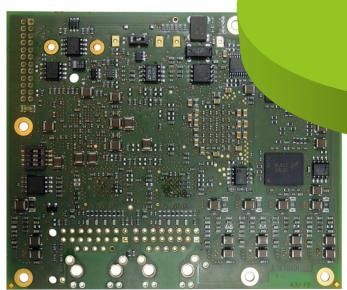

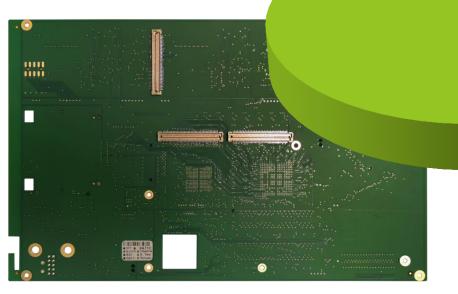

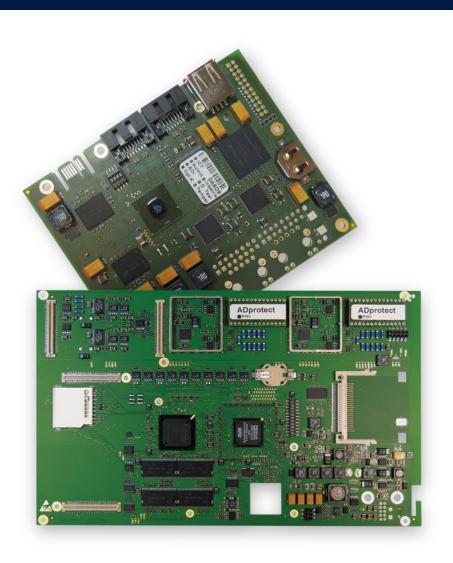

Beispiel Gold2

Beispiel ADwin Pro2

Vertrieb

JÄGER

Computergesteuerte Messtechnik GmbH

www.ADwin.de

Entwickeln

Fertigen

Prüfen

Reworking

Röntgen

Reinigen

Fräsen

Kunden können sämtliche Leistungen modular als Einzelleistungen, sowie auch im Komplettpaket entsprechend Ihrer Anforderungen beziehen.

in der elektronischen Baugruppenfertigung

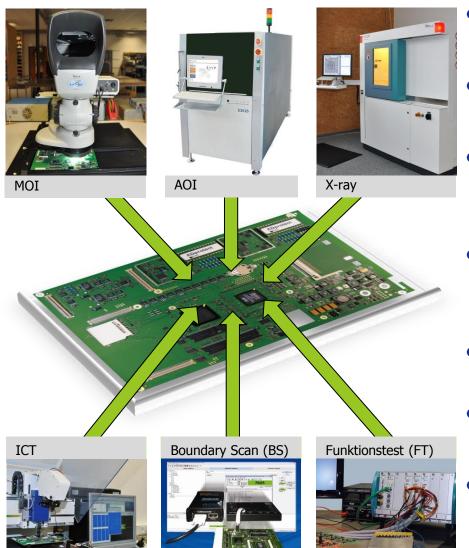

Optische Testverfahren

**Elektrische Testverfahren**

in der elektronischen Baugruppenfertigung

## **Optische Testverfahren**

MOI, AOI, Röntgen 2D/3D, AXI

MOI

AOI

Röntgen 2D/3D

AXI

Bei optischen Testverfahren wird die Verarbeitungsqualität beurteilt. Man ist der Meinung, die Baugruppe funktioniert aufgrund der Verarbeitung.

in der elektronischen Baugruppenfertigung

## **Elektrische Testverfahren**

ICT, Boundary Scan, Funktionsprüfung

**ICT**

Funktionsprüfung

**Boundary Scan**

Funktionsprüfung

Bei elektrischen Testverfahren wird die Funktion der Baugruppe geprüft. Die Baugruppe funktioniert, man kennt die Verarbeitungsqualität nicht.

in der elektronischen Baugruppenfertigung

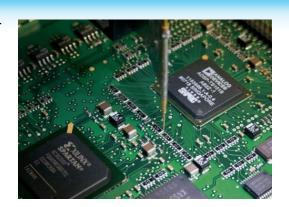

# Elektrische Testverfahren

Allgemein

(Testen in der Schaltung)

**Nadelbett**

Flying Probe

Elektrische Messtechnik ist sehr ähnlich

Unterschiede durch das Kontaktierungsverfahren

Bildquelle: Agilent, SPEA November 2019

## ICT (IN-CIRCUIT-TEST)

Allgemein

## **Teststrategie:**

- Einzelne Bauteile und Netze werden separat getestet, ohne Berücksichtigung der Gesamtfunktion

- Fehler an einzelnen Bauteilen bzw. Netzen können gefunden werden

## Was wird getestet?

- Kontaktierungstest

- Kontakt zwischen Messsystem und Prüfling

- Kurzschlusstest

- •Kurzschlussprüfung zwischen den Netzen

- Widerstandsmessung

- 2-6 Drahtmessung für verschiedene Genauigkeiten und Guarding

- •Guarding, separieren von Bauteilen

- Vektortest

- •Testen von kombinatorischer Logik verliert an Bedeutung wegen der komplexen Bausteinen wie Mikrokontroller, Speicher, programmier- barer Logik, Schnittstellenbausteine usw.

- Feldstärkentest

- •Testen der Verbindung zum Bauteil

- Netzcharakteristik

- Impedanztest

## ICT (IN-CIRCUIT-TEST)

Allgemein

## **Allgemeine Vorteile**

- Der Test der Baugruppe ist mit Nadelbett schnell möglich

- Flying Probe hat eine höhere Flexibilität

- Es muss nicht die komplette Funktion der Baugruppe dem Bediener / Fertiger bekannt sein (Es werden einzelne Bauteile und Netze geprüft)

- Digitale wie analoge Baugruppen lassen sich gleichermaßen testen

- Die Baugruppe ist beim Testen spannungslos, im Fehlerfall tritt keine Schädigung der Baugruppe oder der Bauteile auf

- Hohe Testtiefe aller Netze und Bauteile wird erreicht\*

## Allgemeine Nachteile

- Hohe Taktfrequenzen, impedanzkontrollierte Leitungen grenzen die Möglichkeiten von zusätzlichen Testpunkten im Layout ein

- Testen von Flex-Leiterplatten wegen der Kontaktierung

- Messung von niedrigen/hohen Induktivitäts-, Kapazitäts- und Widerstandwerten (lange Wege mit Prüfleitungen und Schaltmatrix) z.B. Abblockkondensatoren

- Leitungen und Anschlüsse, die komplett verdeckt verlaufen, können nicht getestet werden (Schlupf)\*

- Zunehmende Problematik beim Kontaktieren wegen der Miniaturisierung und verdeckter Lötstellen\*

\* Der Erfolg des Testverfahrens hängt wesentlich von der Testabdeckung (Kontaktierung) ab

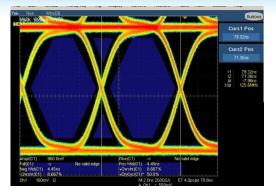

Allgemein

#### Merkmale

- Knotenimpedanzanalyse nach Lissajou (Netzimpedanzanalyse)

- Tischgerät für Muster- u. Kleinserien

- Eine Nadel

- Test 70 100 Netze / Minute

- CAD-Import, Schnittstelle zu 30 CAD-Systemen

- Anregung von Netzen mit verschiedenen Spannungen und Frequenzen

- Testadapter ist nicht notwendig

- Golden Board Verfahren

Allgemein

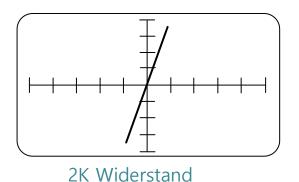

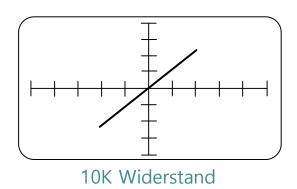

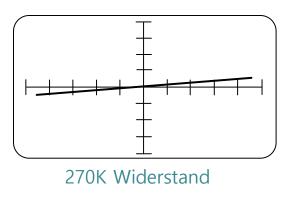

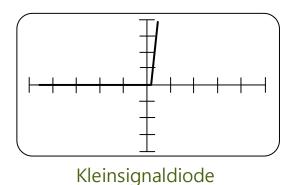

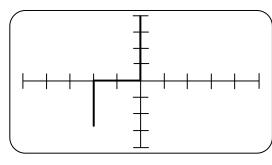

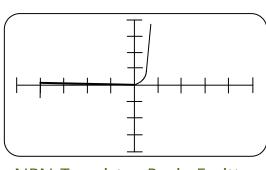

## Darstellung der einzelnen Bauteile

Kennlinie von unterschiedlichen Widerständen

Kennlinie von verschiedenen Halbleitern

8.2V Zenerdiode NPN Transistor Basis-Emitter

Bildquelle: POLAR November 2019

Allgemein

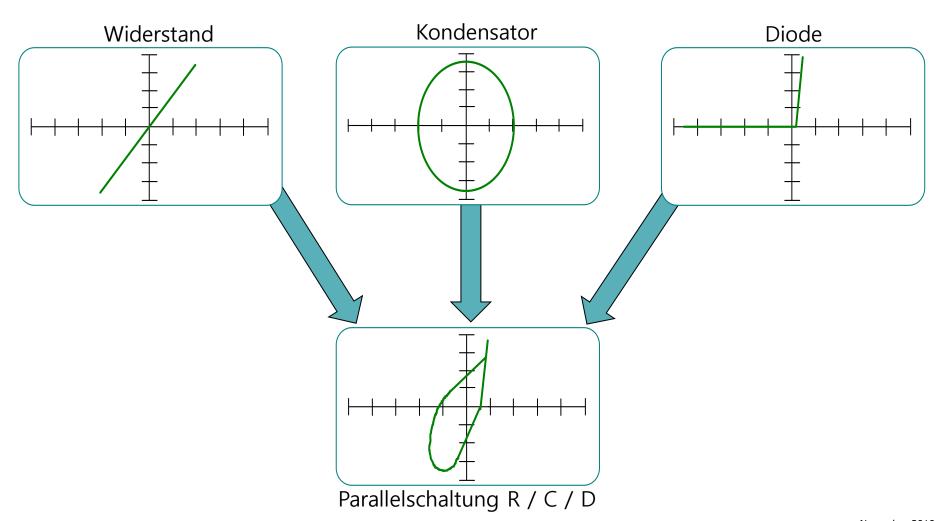

## Darstellung einer Parallelschaltung

Bildquelle: POLAR

November 2019

#### Allgemein

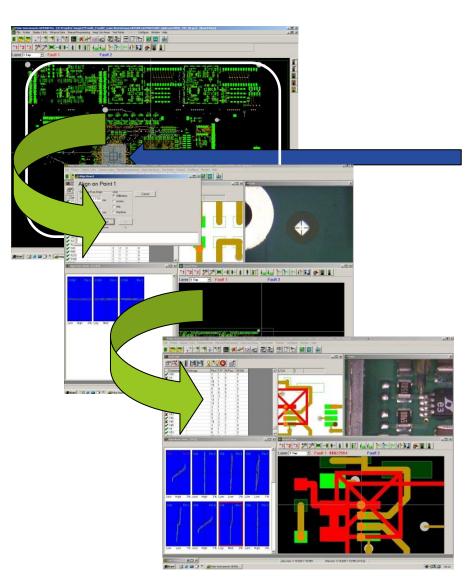

## Vorgehensweise Testprogrammerstellung

- Einlesen der CAD-Daten

- Definition von Sperrflächen und Anschlüsse, die nicht zu kontaktieren sind

- Einlernen der Referenzmarken

- Festlegen der Kontaktierungsposition

- Zeitoptimierung beim Abtasten in niedriger Flughöhe

- Testpunkte möglichst auf eine Seite legen mit niedriger Bauteilhöhe

- Referenzbaugruppe mehrfach zum überprüfen der Kontaktierung einlesen

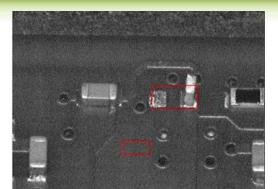

## Fehlerbild: ICT Tombstone

## Fehlerbild: ICT Kurzschluss

- Entscheidend ist der Unterschied zwischen der eingelernten und gemessenen Signatur

- Über das eingeblendete Layout kann das betroffene Netz angefahren und auf dem Monitor überprüft werden

#### Vorteile

- System findet typische Fertigungs- und Bauteilfehler

- Keine Bauteilbibliothek notwendig

- Technologieunabhängig (SMD/THT)

- Test im stromlosen Zustand

- Einfache und schnelle Programmierung

- Es ist kein Testadapter notwendig

- Kein Guarding (elektrisches Separieren von Bauteilen)

- Jedes Netz wird nur einmal getestet

- Kontrolle der Prüftiefe schon bei der Layouterstellung leicht und schnell möglich

- Bauteilanschlüsse und DKs können zur Kontaktierung verwendet werden (Prüfpads sind nur für verdeckte Leitungen notwendig)

#### **Nachteile**

- Erkennt keine bauteilinterne Fehler von Ics

- Misst keine Bauteiltoleranzen

- Erkennt keine dynamische und thermische Fehler

- Bei einer Abweichung muss der Fehler vom Bediener interpretiert werden

- Niedrige Testgeschwindigkeit

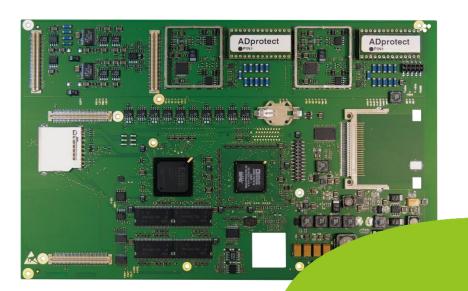

Baugruppe Gigabit-Ethernetmodul

## **Baugruppe Gigabit-Ethernetmodul**

Gesamt 505 Netze (Top + Bottom)

25 Netze (5%) nicht kontaktierbar

- 480 kontaktierbare Netze

- 25 nicht zugängliche Netze

Baugruppe Gigabit-Ethernetmodul

#### Warum sind die Netze nicht erreichbar?

- 26 ICs auf der Baugruppe

- 6 BGA 2x2 Stück gegenüber TOP/BOTTOM

- 8 QFN

- 12 weitere IC's kontaktierbar

- Über 50% der IC's nicht direkt kontaktierbar

- 809 Bauteile (Top 195 Bottom 614)

- Baugruppengröße 99 x 80 mm²

- Durchschnittlich 5,1 Bauteile/cm²

- Multilayer (Leiterbahnen laufen verdeckt)

- Design für hohe Frequenzen

- Trotz der Designrichtlinien und Kontrolle während der Layouterstellung lassen sich nicht mehr alle Netze kontaktieren

- Keine 100% Baugruppenprüfung mit ICT möglich

- Testzeit Flying Probe ICT 2-seitig

7 Minuten

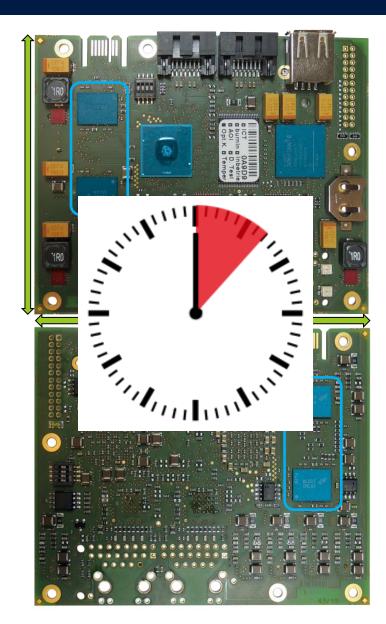

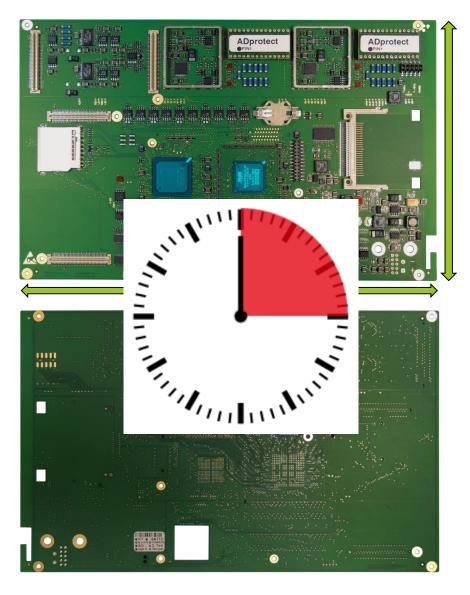

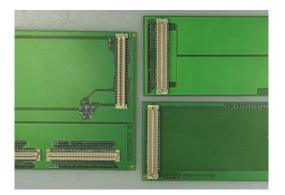

Baugruppe Gold2 Main

## **Baugruppe Gold2 Main**

Gesamt 1125 Netze (Top + Bottom)

100% Netze kontaktierbar

■ 1125 kontaktierbare Netze

Baugruppe Gold2 Main

#### Warum sind alle Netze erreichbar?

- 56 ICs auf der Baugruppe

- 2 BGA

- 6 QFN

- 48 weitere ICs kontaktierbar

- 939 Bauteile (Top 939 Bottom 4)

- Baugruppengröße 154 x 246 mm²

- Durchschnittlich 1,2 Bauteile/cm²

- Multilayer (8-lagig)

- Eine 100% Baugruppenprüfung mit ICT ist möglich

- Testzeit Flying Probe ICT 2-seitig

15 Minuten

## Hier bestand für uns Handlungsbedarf

- Prüfabdeckung

- Testzeit (Maschinenauslastung)

## Was tun?

- weiterer Tester

- schnellerer Tester

## **ODER**

• Überprüfung der Teststrategie

#### Allgemein

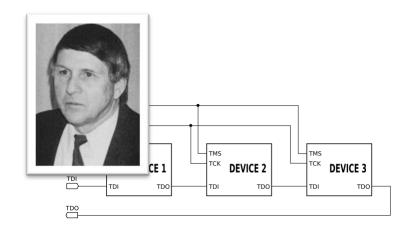

#### Historie

- ➤ 1973 Ed Eichelberger von IBM, erste Erfindung mit Patent zum Zugriff auf Ein- u. Ausgängen von Speicherzellen (Testen von Chips)

- ➤ **1985** Gründung Joint European Test Action Group

- 1986 traten weitere Firmen aus Nordamerika zu und der Name wurde geändert in JTAG (Joint Test Action Group). Speicherelemente wurden an die Bauteilgrenze (at boundaries) eingebracht, was die Möglichkeit der Baugruppenprüfung geschaffen hat

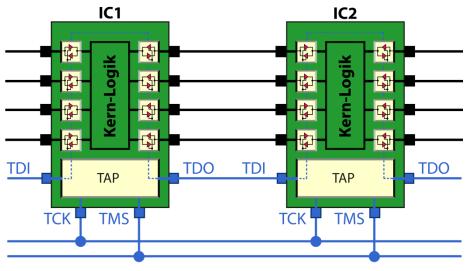

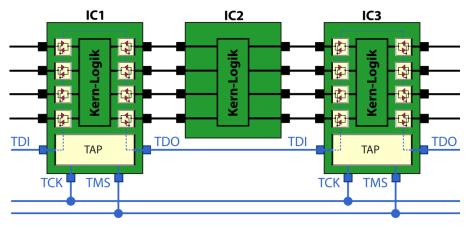

## Allgemeines zu Boundary Scan

- Boundary Scan und JTAG ist das gleiche

- Boundary Scan ist ein digitales Testverfahren, was aber nicht bedeutet, dass nur digitale Systeme getestet werden können.

- Boundary Scan ist ein Testverfahren ohne Kontaktierung der Netze

Bildquelle: Wikipedia November 2019

Allgemein

## Allgemeine Hinweise

- Auf der Baugruppe muss mindestens ein Boundary Scan fähiges Bauteil vorhanden sein

- Boundary Scan benötigt die Spannungsversorgung und die funktionsfähige Boundary Scan Kette

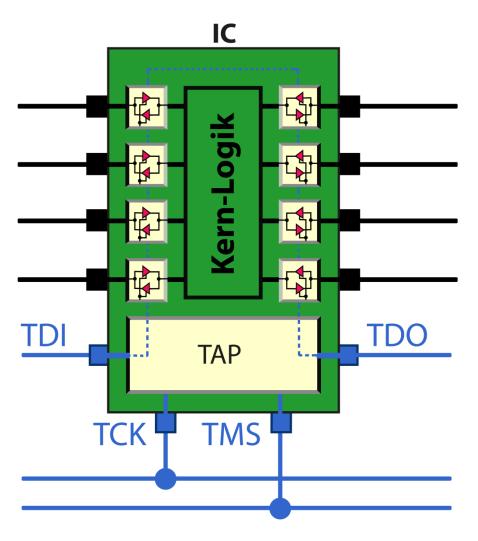

- Die BS-Zelle befindet sich zwischen der Kernlogik und dem Anschlusspin

- Mit der BS-Zelle besteht die Möglichkeit den Bauteilpin eines Baustein losgelöst von seiner normalen Funktion zu betreiben (Eingang, Ausgang oder Steuerzelle)

- BS ist ein langes Schieberegister (Bits werden von Zelle zu Zelle geschoben). Ein Signalwechsel bei 1000 BS-Zellen und einem Takt von 10MHz dauert 100µs das entspricht 10.000 Signalwechsel/Sek.

- Testzeit ist linear zur Taktfrequenz (bis zu 80 MHz)

- Der TAP (Test Access Port) stellt die Verbindung zwischen den Boundary Scanzellen und der Außenwelt her

Allgemein

#### Welche Bauteile lassen sich testen?

- Jeder Boundary Scan fähige Baustein

- Boundary Scan fähiger Baustein ist in einer BDSL-Datei (Boundary Scan Description Language) beschrieben

- Die BDSL-Datei erstellt der Bauteilhersteller, er kennt am besten seinen Baustein und die daraus entstehenden Testmöglichkeiten

- Boundary Scan Zelle muss vor dem Betrieb konfiguriert werden (wird von der Software übernommen)

- Ein einfacher Test ist die Prüfung von Boundary Scan fähigen Chips in einer BS-Kette

- So einfach ist die Baugruppenprüfung leider nicht, typische Baugruppen bestehen auch aus zahlreichen nicht BS fähigen Chips

#### Allgemein

## Welche Bauteile lassen sich noch testen?

- Chips ohne BS werden getestet wie z.B. Treiber, Logische Gatter, AD/DA-Wandler

- Flüchtige Speicherbausteine (DDR 2/3 u. SRAM)

- BDSM-Datei (Boundary Scan Description Mode) ist notwendig, wird vom Systemlieferant erstellt

- Integrierte und separate Flash Bauteile lassen sich programmieren (Geschwindigkeit langsam)

- Chips werden oft außerhalb der Timingspezifikation betrieben (es funktioniert)

- Widerstände wenn diese an ein BS-Netz angeschlossen sind z.B. Netzabschlusswiderstand, die Bestimmung des Widerstandswert ist nicht möglich (Anwesenheitstest)

- externe Taktgenerator, Bestimmung der Taktfrequenz ist nicht möglich (Schwingungstest)

#### Allgemein

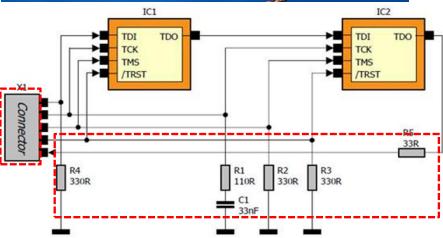

## **Physikalischer Anschluss**

- Anschluss Boundary Scan- und TAP-Controller über USB/Ethernet

- Der physikalische Zugriff erfolgt über vier (fünf) Testanschlüssen (TDI, TDO, TMS, TCK, optional TRST) und die Versorgungsspannung

- Einfache Beschaltung mit wenigen zusätzlichen passiven Bauteilen und dem BS-Anschluss

## Wo liegen die Grenzen?

- Testen von zeitkritischen digitalen Signalen und Systemen, bei Boundary Scan bezieht man sich in der Regel auf den Standard IEEE1149.1

- Testen analoger Bauteile und schneller digitaler Verbindungen, hierzu gibt es die Standards IEEE1149.4 und IEEE1149.6

- Nur begrenzt für analoge und HF-Schaltungen anwendbar, wenn diese losgelöst von BS-Chips arbeiten

Bildquelle: Göpel electronic November 2019

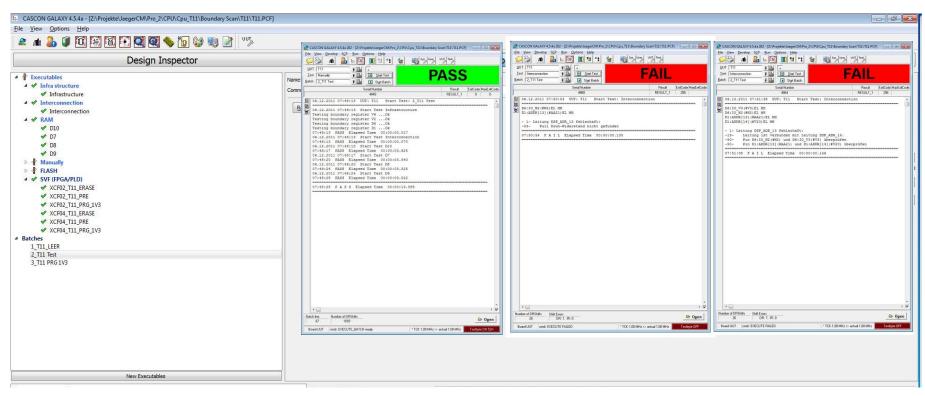

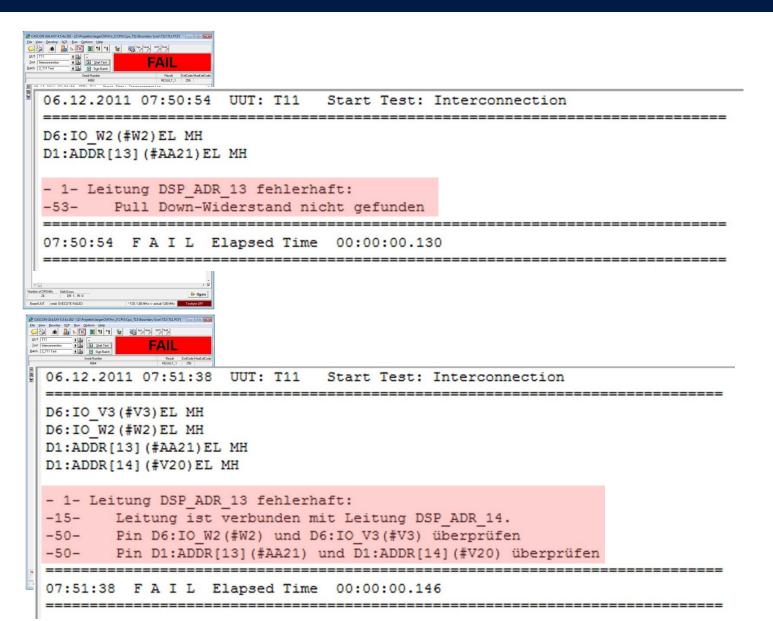

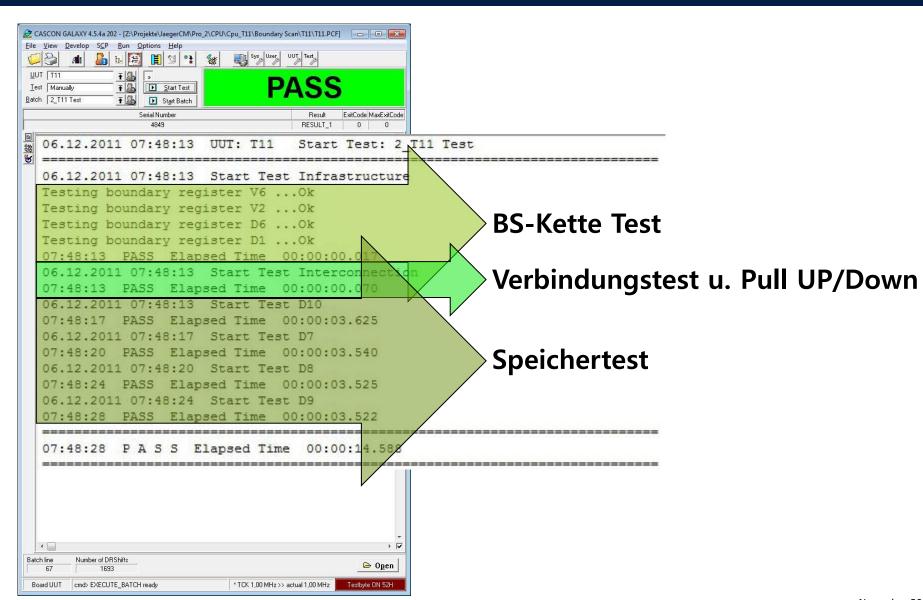

Anwendung

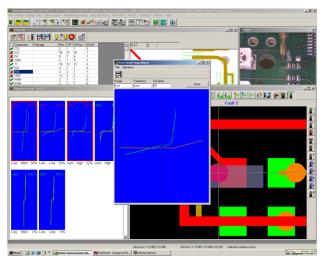

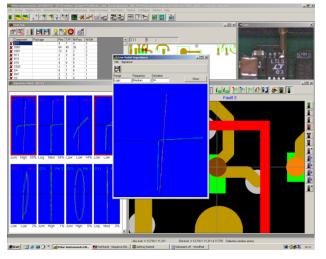

## Anwendungssoftware

- Testprogramm wird größtenteils automatisch mit der Netzliste (Schaltplan), Bauteilmodelle für BS und nicht BS-Bauteile erzeugt

- Konfigurierung der BS-Kette wird von der Software übernommen

- Präzise und schnelle Fehlerlokalisierung

#### Anwendung

#### Anwendung

#### Anwendung

## Baugruppenschnittstelle

- Viel ist mit Boundary Scan möglich, doch was ist mit den Schnittstellen?

- An den Schnittstellen der Baugruppe müssen die notwendigen Vorkehrungen zum Test getroffen werden

- Verbindung der Netze (Ein-/Ausgang)

- Externe Beschaltung

- Kundenspezifische Adapter mit BS

- TAP-Controller mit analogen u. digitalen Ein- und Ausgängen

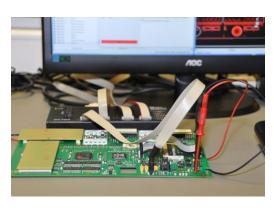

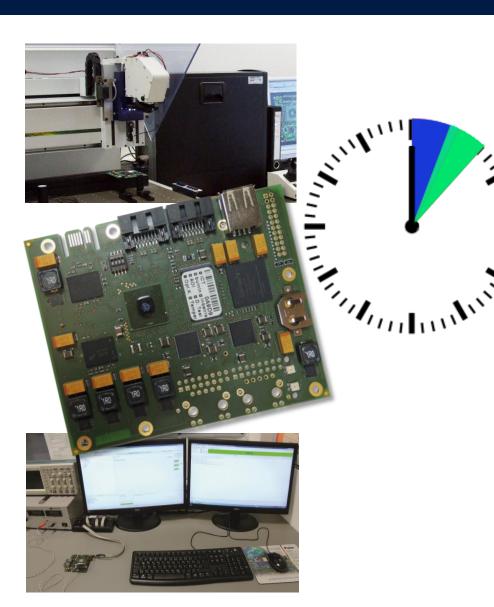

## Funktionsprüfung

Allgemein

## Allgemeines zur Funktionsprüfung

- Der erste Test in der Entwicklung einer Baugruppe unter zusätzlichen Einflüssen wie Temperatur, Klima, Vibration und elektromagnetische Störung / Abstrahlung

- Die Funktion der Baugruppe und elektronisches Verständnis muss vorhanden sein, um ein Test durchzuführen, ist es nicht vorhanden, handelt es sich um eine gut/schlecht Selektion

- Fehler auf der Baugruppe lässt sich nicht klar lokalisieren

- Ist der realistischste Test, der den späteren Verwendungsfall nachbildet

- Funktionsausfälle können protokolliert werden

- Funktionstest sollte mit anderen Testverfahren kombiniert werden

- Was ist mit den Schnittstellen?

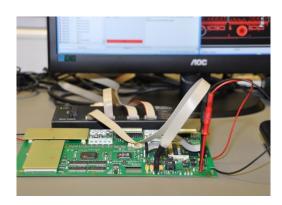

## **Funktionsprüfung**

#### Allgemein

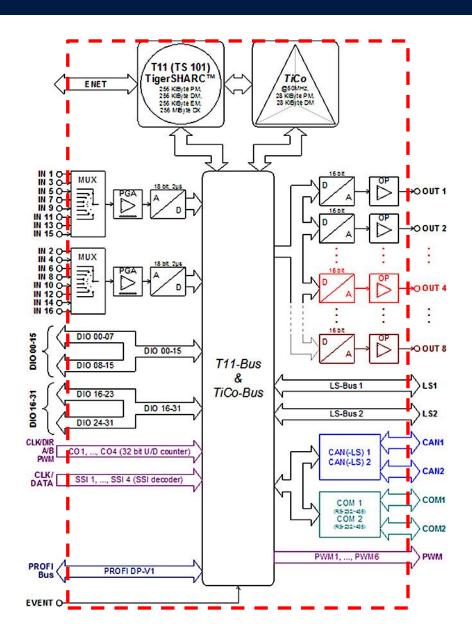

## ADwin Testsystem für schnelle dynamische Prozesse

- Schnittstellen der Baugruppe müssen nachgebildet werden

- analoge Ein/Ausgänge

- digitale Ein/Ausgänge

- Zähler

- Feldbusse

- Temperaturmessung

- Kundenspezifische Schnittstellen

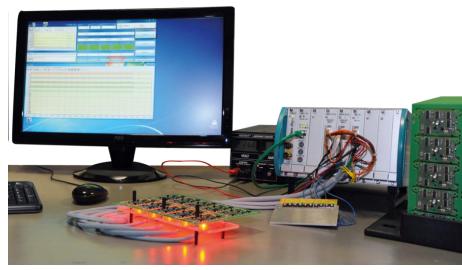

## **Funktionsprüfung**

#### Testsystem

#### Vorteile

- Zeitkritische Abläufe können geprüft werden (Reaktionszeit < 200ns)</li>

- Erkennt thermische und dynamische Fehler

- Auf Verwendung mehrerer Messgeräte kann verzichtet werden (FG, OSZI, DLA)

- Korrelation der verschiedenen Funktionen

- Einfache Programmierung mit ADbasic

- Messwerte werden leicht mit den ADtools grafisch dargestellt

- Schnittstelle zu übergeordneter

Programmiersprachen und Testsystemen

- Automatisierter BURN-IN (Langzeittest) unter definierten Einflüssen für mehrere Baugruppen gleichzeitig

#### **Nachteile**

- Testprogramme werden nicht automatisch generiert, der Test muss genau auf den Prüfling abgestimmt werden

- Es muss sichergestellt sein, dass alle Funktionen der Baugruppe getestet werden (ein abgeschlossenes Testprogramm)

- Programmierkenntnisse sind erforderlich

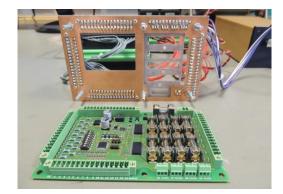

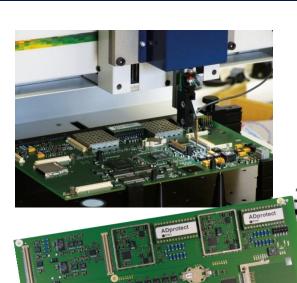

## Adaptierung zur Unterstützung der Testverfahren

Allgemein

## Mehraufwand an Testleiterplatten und Mechanik

Funktionstest Kabel zum Verbinden der Schnittstellen

Funktionstest Testadapter mit Nadel, gefräst aus FR4 Material

Boundary Scan Verbinden der Schnittstellenanschlüsse mit Adapterplatine

Boundary Scan

Verbindungstest

Bussystem

Adapter zum

Testen der

internen und

externen Busse

Boundary Scan und Funktionstest benötigen Mehraufwand

## **Elektrische Baugruppenprüfung**

Kombination der Testverfahren

#### **Aufwand FP-ICT**

- Gesamt 505 Netze (Top + Bottom)

- 25 Netze (5%) nicht kontaktierbar

- Testzeit 7 Minuten

#### **Aufwand FP-ICT + BS**

- FP-ICT Testzeit der nicht BS-Netze

3,5 Minuten (Top + Bottom)

- BS-Testzeit restliche Netze mit Speichertest 0,75 Minuten

- <u>Alle</u> Netze werden getestet

- Gesamttest 4,25 Minuten

## **Ersparnis**

- 2,75 Minuten das entspricht 40

- 3,5 Minuten mit Verschachtelung

50%

## **Elektrische Baugruppenprüfung**

Kombination der Testverfahren

#### **Aufwand ICT-FP**

- Gesamt 1125 Netze (Top + Bottom)

- 100% Prüfabdeckung mit FP-ICT

- Testzeit 15 Minuten

#### Aufwand FP-ICT + BS

- FP-ICT Testzeit der nicht BS-Netze5 Minuten (nur Top)

- BS-Testzeit mit Speichertest 2,5 Minuten

- <u>Alle</u> Netze werden getestet

- Gesamttest 7,5 Minuten

## **Ersparnis**

- 7,5 Minuten das entspricht **50%**

- 10 Minuten mit Verschachtelung **67%**

## Elektrische Baugruppenprüfung

Kombination der Testverfahren

#### Kalibrieren und Dauertest

- Autarke Kalibrierung über einen längeren Zeitraum von den 18 Bit AD/DA-Wandler

6 Minuten für 8-20 Trimmer

- Sämtliche Kalibrierdaten werden protokolliert und in die Datenbank übernommen

- Funktionstest / Burn-In aller Schnittstellen und Anschlüsse, diese werden über 24 Std. getestet und am Schluss nochmal kalibriert

- Im Testprogramm werden alle Funktionsbereiche abgebildet und getestet, Fehlfunktionen werden eingegrenzt

- Testprogramm ist für den Servicefall ebenfalls geeignet

- Testprogramm steuert gleichzeitig die Temperaturmesskammer, zur Korrelationen zwischen Fehler und Temperatur

## **Investitionen Prüfsysteme**

## **Investition Flying Probe ICT**

- Reines FP ICT System 85K€

- Baugruppen werden seriell abgearbeitet

- Es wird nur eine Baugruppe getestet

## **Investition Boundary Scan**

- Entwicklungs- und Testsystem 10-25K€

- Es können bis zu 8 Baugruppen parallel getestet und programmiert werden

## **Investition ADwin Prüfsystem**

- PC-Einsteckkarte ab 4k€ inkl. Software

- 19" Testsystem 10-20k€ je nach Ausbau (jederzeit erweiterbar)

- Es können mehrere Baugruppen gleichzeitig getestet werden

Bildquelle:Mellimage - Fotolia November 2019

#### Kombination der Testverfahren

#### Allgemein

- Das Testverfahren, das alle Fehler findet, gibt es (noch) nicht

- Eine Kombination von verschiedenen Testverfahren ist notwendig (min. zwei)

- Testverfahren können in einem System kombiniert oder autark durchgeführt werden

- Jede Baugruppe ist anders, die Teststrategie muss für jede Baugruppe neu geprüft werden

- Doppelprüfung möglichst vermeiden

- Teststrategie bereits im Prototypenstatus überprüfen

- Regelschleife beim Erkennen von Fehlern, Lücken in der Baugruppenprüfung schließen

Bildquelle: Viscom

November 2019

## Design zum Testen von Baugruppen

Allgemein

## Designvorschläge

- Für Boundary Scan muss sichergestellt sein, dass die Spannungsversorgung und die Boundary Scan Kette funktioniert

- Standardisierter Anschluss für Boundary Scan (Firmenintern)

- Design auf Kontaktierung mit ICT überprüfen

- ICT Kontaktierung möglichst auf eine Baugruppenseite TOP oder BOTTOM legen

- Leichte Anschlussmöglichkeit für den Funktionstest (keine Lötverbindung)

- Vermeiden Elektromechanischer Komponenten wie z.B. Trimmer und DIP-Schalter

## Prinzipielle Punkte zur elektrischen Baugruppenprüfung

- Testen von Baugruppen muss man wollen vom Management über die Entwicklung bis zur Fertigung

- Testen kostet erst einmal Zeit und Geld, gespart wird später

- Gespür für Fehler und Auswirkungen bei dem Prüfpersonal wecken

- Jede Fertigung intern/extern hat andere Möglichkeiten und Vorlieben

- Fertigung / Dienstleister frühzeitig einbinden, um das Design entsprechend den Möglichkeiten und den vorhandenen Testsystemen anzupassen

- Testen der Baugruppe beginnt bereits bei der Entwicklung, Schaltplan / Layout / VHDL / Mechanik

- Prüfadapter / Kabel in die Entwicklung einbeziehen

- Elektronisches Verständnis und strukturiertes Arbeiten muss vorhanden sein

## Resümee

- Es ist entscheidend mit welchem Testverfahren und Strategie man prüft um eine möglichst hohe Prüfabdeckung zu erreichen

- Mit der richtigen Prüfstrategie lassen sich Kosten einsparen und die Prüftiefe erhöhen

- Elektrische Baugruppenprüfung muss bereits bei Projektbeginn fest eingeplant und verfolgt werden

- Elektrische Prüfung ist zukunftsweisend für moderne Baugruppenfertigung

## Vielen Dank für Ihre Aufmerksamkeit

Wir bieten Ihnen eine perfekte Dienstleistung in jedem Detail – und behalten zugleich das "Ganze" immer im Blick.

#### **ANDREAS KRAUS**

Gesellschafter

Geschäftsführer

www.kraus-hw.de

#### Ostring 9 c

63762 Großostheim/Ringheim

PHONE +49 6026 9978-78

+49 6026 9978-99

MOBIL +49 171 7828112

E-MAIL akraus@kraus-hw.de